Last year Amanda Whittemore and I had the pleasure of attending a 2 day seminar “IC Fab East”in

Jim: What defects in FEOL or BEOL could show up during packaging?

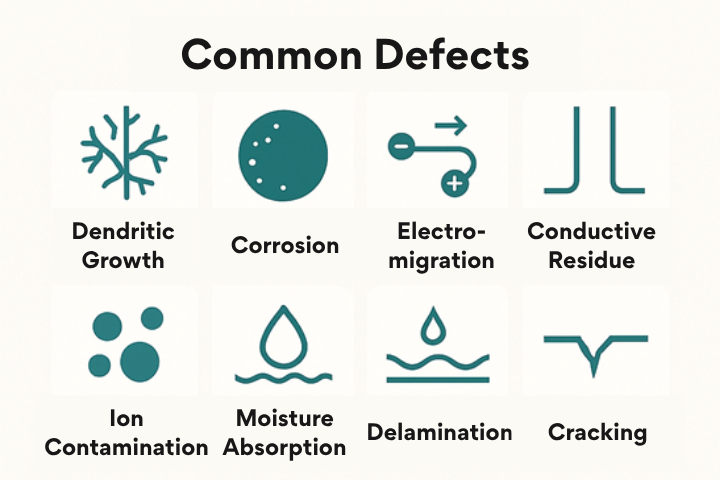

Ernest: First and foremost, cracking of the chip from too much stress during packaging. Need to assess plastic molding and its resistance to avoiding stress cracking of the chip. Witness recent game maker that reported thermal loads cracked chip. Dicing before packaging can damage the chip and cause failure during packaging. Besides that, when one packages and subjects to burn-in, any defect in front or back end can manifest itself as a fail as usually one exercises circuits never exercised before. Thus near opens, shorts, BEOL voids etc. can all propagate to failure. Stress from wire bonding can crack the low-k chip whose modulus is far below quartz.

Jim: Are there any chemicals that could remain on the wafer surface and hinder wire bonding, bumping or wafer-level packaging?

Ernest: Sure, drying residue will hinder wire bonding. Here I assume that we are bonding to Al bonding pads. Stains of any kind will not allow a bond to occur.

Jim: I noticed a large cross-section of engineers attending your class, are there any notably interesting attendees you’ve hosted?

Ernest: They are all interesting. They are from user companies like Microsoft and Cisco and from Vendors such as LAM and KLA. My pleasure is in getting people so they really understand the material.

Ernest has another class coming up October 6th and 7th. If you are interested in the IC Fabrication and Yield course, you can contact Ernest at [email protected]