7月份,我有幸去了景色迷人的三藩市(San Francisco)参加Semicon West展会,并听了“The 2.5 & 3 D packaging landscape for 2015 and beyond”的技术讲座。 这是我第一次参加半导体方面的展会,虽然2.5D 和3D packaging等相关词语听多了,但是真正含义是什么,也是直到最近才真正了解。 上周Triquint Semiconductor的齐权博士(Dr. Quan Qi)给我进一步讲解后,才又“豁然开朗”了许多。

简单来说吧,2.5D就是还要依靠一层Interposer来叠加,而不是直接logic & memory叠加到substrate上面。 而3D packaging 就能真正做到logic & memory到substrate上的直接多层叠加。齐博士给我举了一个很好的例子为什么现在很多公司还是在做2.5D,而不是3D,主要是3D有很大的CTE Mismatch. 比如说Logic & Memory的CTE 是3ppm, 但是substrate是17ppm。 在如此微型化的今天,很多小球(sphere)和pad就会因为CTE的大差别而错位。 如果引入了一层interposer, 就能够缓冲CTE mismatch 的问题。

2.5D 和3D packaging各自的优劣势,存在的问题和挑战,专家们都在这个演讲稿里面有自己详细的分析,如果有兴趣,很值得阅读参考:“The 2.5 & 3 D packaging landscape for 2015 and beyond”

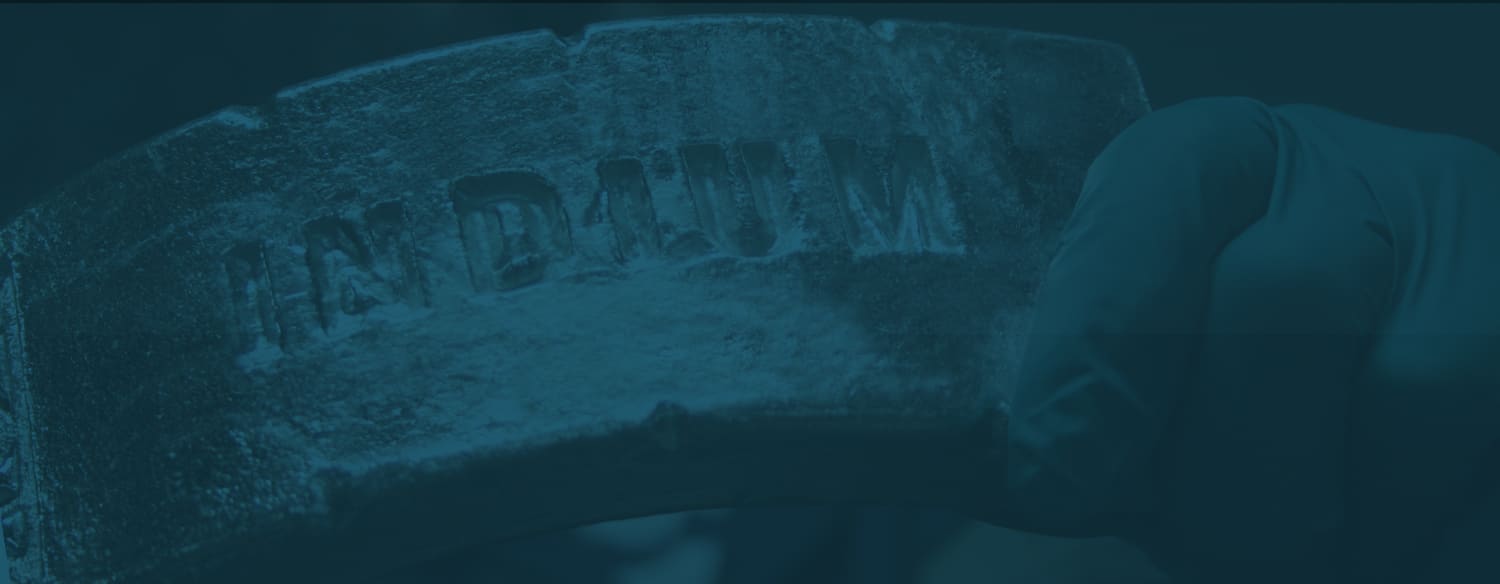

Indium Corporation能够为2.5D 和3D packaging提供各种Flip-Chip, Package-on-Package, 和Ball-Attach 之间的连接材料和解决方案。 欢迎参考: http://www.indium.com/products/semiconductorpackagingassembly.php

Cheers!

Picture Resource: Dr. John Xie’s (Altera Coproration) presentation in Semicon West 2012.